Verilog快速入门

(1) 四选一多路器

(2)异步复位的串联T触发器

(3)奇偶校验

(4)移位运算与乘法

(5)位拆分与运算

(6)使用子模块实现三输入数的大小比较

(7)4位数值比较器电路

(8)4bit超前进位加法器电路

(9)优先编码器电路①

(10)用优先编码器①实现键盘编码电路

(11)8线-3线优先编码器

(12)使用8线-3线优先编码器实现16线-4线优先编码器

(13)用3-8译码器实现全减器

用3-8译码器实现全减器

Verilog快速入门一、题目描述二、解析与代码一、题目描述

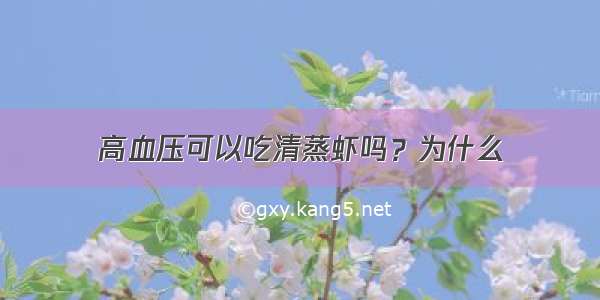

请使用3-8译码器(其功能表见上一篇)和必要的逻辑门实现全减器,全减器接口图如下,A是被减数,B是减数,Ci是来自低位的借位,D是差,Co是向高位的借位。

3-8译码器代码如下:

module decoder_38(input E,input A0,input A1,input A2,output reg Y0n , output reg Y1n , output reg Y2n , output reg Y3n , output reg Y4n , output reg Y5n , output reg Y6n , output reg Y7n );always @(*)beginif(!E)beginY0n = 1'b1;Y1n = 1'b1;Y2n = 1'b1;Y3n = 1'b1;Y4n = 1'b1;Y5n = 1'b1;Y6n = 1'b1;Y7n = 1'b1;end else begincase({A2,A1,A0})3'b000 : beginY0n = 1'b0; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b001 : beginY0n = 1'b1; Y1n = 1'b0; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b010 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b0; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b011 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b0; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b100 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b0; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b101 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b0; Y6n = 1'b1; Y7n = 1'b1;end 3'b110 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b1;end 3'b111 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b0;end default: beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;endendcase end end endmodule

二、解析与代码

首先把全减器真值表写出来:

module decoder1(input A,input B,input Ci ,output wire D,output wire Co );wire Y0n,Y1n,Y2n,Y3n,Y4n,Y5n,Y6n,Y7n;decoder_38 decoder_38_inst(.E(1'b1),.A0(Ci),.A1(A),.A2(B),.Y0n(Y0n),.Y1n(Y1n),.Y2n(Y2n),.Y3n(Y3n),.Y4n(Y4n),.Y5n(Y5n),.Y6n(Y6n),.Y7n(Y7n));assign Co = (~Y1n)|(~Y4n)|(~Y5n)|(~Y7n);assign D = (~Y1n)|(~Y4n)|(~Y2n)|(~Y7n);endmodule

![[Verilog]半减器 全减器设计](https://gxy.kang5.net/uploadfile/img/2018/09/14/c0b1b13d36d106ed0d506afaf56e6ec1.jpg)